Enabling a New Era for Flash in the Data Center

Next Gen data centers require highly deterministic, low latency and cost effective storage that can only be realized with Flash memory. But every Flash SSD solution available today is based upon a Flash-Translation-Layer (FTL) that introduces expensive overhead, unpredictable latency spikes, and suboptimal performance that prematurely wears out the Flash media.

Symphonic is a type of Software-Defined Flash that creates a new paradigm for Flash memory management that we call Cooperative Flash Management (CFM). System software, e.g., file systems, block virtualization managers, or object/key value stores have comprehensive capabilities to intelligently manage storage media. But this system software is not equipped to directly perform some of the unique processes required to manage Flash memory.

Replacing the SSD FTL, Symphonic includes a combination of host-side software libraries and SSD firmware that enables system software to cooperatively perform Flash management processes to realize the full potential of Flash storage. The Symphonic functionality includes configurable address mapping, garbage collection, wear leveling, and reliability features that turn the SSD into an offload engine while operating in host address space. The result is a redistribution of host/device responsibilities that removes an inefficient abstraction layer to dramatically improve Quality-of-Service, performance, cost, and endurance while providing the functionality of a data center class product.

Offload Accelerator Engine

- Symphonic firmware turns the SSD into an offload accelerator engine

- State machines are integrated with mapping and translation tables to perform operations and generate/maintain comprehensive metadata

- Counters track valid/release states with firmware performing heuristic analysis to provide fine grain qualitative range fragmentation metrics

- Provides linear scalability across metrics as additional SSDs are added to the system

Cooperative Garbage Collection

- Garbage collection (copy/move/erase) operations executed by Symphonic firmware, performed entirely on SSD

- Processes scheduled and controlled by host and performed in host address space

- Eliminates additional system copying and overhead, freeing host resources

Wear Leveling & Reliability

- Wear leveling and bad block management performed by Symphonic firmware on the SSD with ECC

- Processes integrated with garbage collection, transparently to the host

- Optional mode to support global host-based wear leveling

- Fault tolerance and support for ACID requirements

- Provides RAS capabilities such as hot swap and FRU functionality

- Enables vendor supported warranties

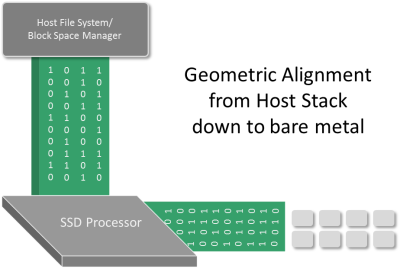

Geometry Emulation

- Virtualizes topology of physical NAND array, exporting an emulated version of device geometry to the host

- Abstracts lower level NAND attributes, releasing host from managing NAND constraints

- Maintains symmetric alignment from host down through NAND array

- Minimizes collisions and unpredictable latency spikes while providing maximum parallelization

- Forward Compatibility to help ‘future proof’ system software from evolutionary changes in geometry and vendor-specific NAND attributes

Address Configurator

- Symphonic libraries provide extensible connectivity from host space management through the system to SSD firmware

- Facilitates host integration and minimizes modifications to existing host software

- Enables readily optimizing opposing performance and efficiency constraints unique to Flash memory

- Preserves host data layout optimizations through to physical media

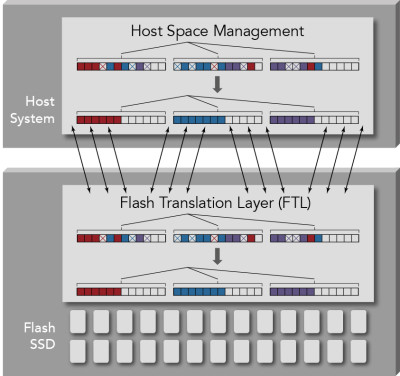

FTL SSD

- Redundant levels of space management, lookup and locking penalties

- Two levels of write amplification

- Dislocation from two asynchronous processes

- Barrier to realizing host intelligence, data locality and layout optimizations on media and across storage volumes

- Requires additional Flash capacity overprovisioning

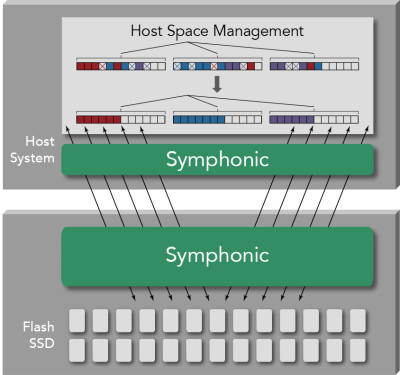

Symphonic SSD

- Single level of space management, lookup and locking penalties

- One level of write amplification

- Management processes are coherent

- Host’s global intelligence, scheduling, knowledge of data locality and layout optimizations realized on media and across storage volumes

- Minimizes capacity overprovisioning

Software that provides the Performance of fully Custom Hardware

By taking a system-level approach to software architecture, Symphonic utilizes SSDs to provide the performance, latency, and endurance that can otherwise only be achieved with fully custom hardware platforms.

Symphonic’s coherency and geometric alignment enables massive parallelization that avoids collisions and unpredictable latency spikes.

Improving Endurance (TCO): Reduces Total

Write Amplification factor 75%

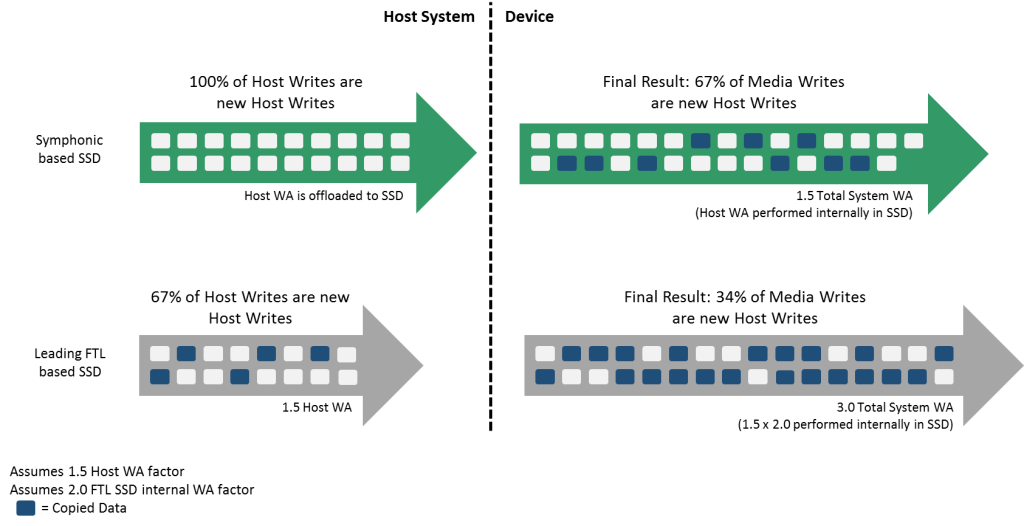

Because Symphonic operates in host address space and performs garbage collection processes coherently under host control, only one level of write amplification occurs, instead of the double write amplification penalty incurred with FTL SSDs.

And because Symphonic firmware turns the SSD into an offload engine, the host’s write amplification is transferred onto the SSD.

So 100% of host writes to the Symphonic SSD are for new data, eliminating costly copy/move overhead between the host and SSD.

The final result is not just dramatically higher performance, but fewer writes to the Flash media which minimizes wear out and extends usable product life.

Less overprovisioning reduces acquisition costs

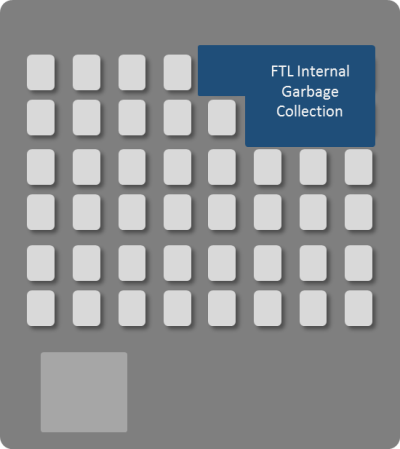

Enterprise class FTL SSDs typically reserve 15% to 30% of the SSD’s raw Flash just for performing internal garbage collection operations. This capacity allocation is required to reduce unpredictable latency spikes (QoS), wear out, and improve IOPS/bandwidth.

Symphonic does not require overprovisoning for internal garbage collection, and consuming the typical associated 15% to 30% of reserve capacity, but provides dramatic improvements in each of the same metrics this overprovisoning attempts to address:

– Magnitude improvement in unpredictable latency spikes

– Typically reduces write amplification (wear out) factor by 75%

– More than 80% improvement in IOPS/Bandwidth